## **SOLUTION BRIEF**

**Functional Safety**

# Qualified Functional Safety Data Package

### Reduce Development Time, System Complexity, and Certification Risk

#### Safety Data Package Contents:

- Silicon Integration How to qualify devices using the reliability report

- Tools and Tool Flow How to use Intel<sup>®</sup> Quartus<sup>®</sup> Prime software and develop FPGAs according to IEC 61508

- Suggested RTL coding guidelines for FPGA development

- Diagnostic IP with IEC 61508 documentation and source code: single event upset (SEU) test, clock check, and cyclic redundancy check (CRC) test modules

- Intel Quartus Prime Standard software version 17.0.2

- Intel-qualified devices up to Cyclone<sup>®</sup> V, Cyclone IV, Arria<sup>®</sup> V, and Stratix<sup>®</sup> V FPGAs and MAX<sup>®</sup> 10, MAX V, MAX II and MAX II Z CPLDs

- Intel IP including Nios<sup>®</sup> II embedded processor

- The latest FPGA device reliability report

#### **Summary**

Industrial automation, transportation, the smart grid, automotive, military, aerospace, and medical require machinery and products are highly reliable, and certified for functional safety. Safety is a central requirement when you develop machinery that must comply with worldwide established safety standards such as IEC 61508 and ISO 26262.

When you develop a safe product, you need to consider safety as a core system functionality. Design challenges include:

- Adopting quality management standards, a "safe" design methodology, and safety concepts

- Accounting for additional project effort (time and technology), resulting in longer time to market and higher cost of ownership

#### **Impact of Functional Safety**

Typical design steps to develop an application, before safety:

Architecture

Component

Application Design

Integration

Development

Selection

Implementation

and Test

Release

If you add some of the required steps to design a safe application and achieve functional safety certification (in yellow), you can see the significant project complexity:

| Project Startup,<br>Risk Analysis |  |  | Validation,<br>Verification<br>Plan |  | IP and Tools |  | Diagnostic | Integration<br>and Test | Safety<br>Validation | Certification | Release |  |

|-----------------------------------|--|--|-------------------------------------|--|--------------|--|------------|-------------------------|----------------------|---------------|---------|--|

|-----------------------------------|--|--|-------------------------------------|--|--------------|--|------------|-------------------------|----------------------|---------------|---------|--|

Having immediate access to qualified semiconductor data, intellectual property (IP), development flows, and design tools from Intel can significantly shorten overall project time by one and one half to two years:

#### **Accelerating Development**

To simplify and speed up the certification process for faster time to market, we worked with TÜV Rheinland and obtained approval for Altera® FPGA devices, IP, our established safety FPGA design flow, and development tools for safety designs up to Safety Integrity Level 3 (SIL3). This certification means that our tools, methodologies, and devices are sufficiently free of systematic errors.

#### INTEL FUNCTIONAL SAFETY DATA PACKAGE CONTENTS

| FUNCTIONAL DATA<br>SAFETY PACKAGE      | BENEFIT                                                          |  |  |  |

|----------------------------------------|------------------------------------------------------------------|--|--|--|

| Intel FPGA Development<br>Methodology  | Qualified, safe design methodology                               |  |  |  |

| Intel FPGA development tools           | Qualified tools                                                  |  |  |  |

| Intel IP                               | Shorter design time, faster debug for safety architecture        |  |  |  |

| Diagnostice IP                         | Shorter design time, faster debug for safety architecture        |  |  |  |

| Device reliability reports, guidelines | Simplifies risk analysis, failuures in<br>time (FIT) calculation |  |  |  |

| Formatted in compliance with IEC 61508 | Seamless integration into product documentation                  |  |  |  |

#### **Intel FPGAs Provide Flexible Safety Solutions**

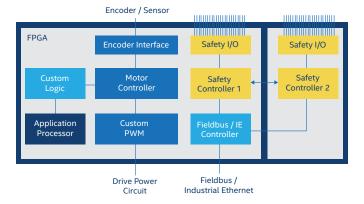

Figure 1 illustrates a typical industrial controller application. It integrates standard ("non-safe") and safety functions with very few board components using FPGA devices, such as the Intel Cyclone FPGA, and a soft processor core, such as the Nios II processor. In this example, all three embedded controllers are Nios II soft-core processors, each with an individual custom peripheral set.

With such a safety-focused architecture for a SIL3 certified application, you can reduce the total cost of ownership, design footprint, and power consumption while meeting the global requirements for functional safety.

Architectures where safety typically is an after-thought often use bolt-on safety option boards and dual microcontroller units (MCUs) that detect system failures. Using an option card significantly increases costs. Integrating a SIL3 "safe" solution in a pre-qualified FPGA with standard application functions on the main board not only lowers the safety cost footprint, but it also enhances system flexibility and shortens development time. It is designed with safety as a core system functionality in mind.

If you are concerned about the lack of flexibility, long development times, or device certification issues that come with traditional safety architectures, Intel FPGAs are the ideal solution.

#### Figure 1. A Typical SIL3 Industrial "Safe" System

TÜV Rheinland Certificate No. 968/EL 850.00/12 Product Order Numbers

Functional Safety Data Package: **IP-ABG-SafetyDP5**

Annual Renewal: **IPR-ABG-SafetyDP5**

#### Learn More

For more information on developing IEC 61508 systems with Intel FPGAs and the Functional Safety Data Package, please contact your local Intel representitive, the nearest distributors' sales office or visit the Functional Safety page at www.Intel.com/safety.

† Tests measure performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks

© Intel Corporation. Intel, the Intel logo, the Intel Inside mark and logo, the Intel. Experience What's Inside mark and logo, Altera, Arria, Cyclone, Enpirion, Intel Atom, Intel Core, Intel Xeon, MAX, Nios, Quartus and Stratix are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. See Trademarks on intel.com for full list of Intel trademarks. SS-1033-4.0 \*Other names and brands may be claimed as the property of others.