Visible to Intel only — GUID: hqw1647318068947

Ixiasoft

Visible to Intel only — GUID: hqw1647318068947

Ixiasoft

7.1.3.5. Dynamic Reconfiguration

To implement dynamic reconfiguration in F-Tile devices, you need to use F-Tile Dynamic Reconfiguration Suite IP in Intel® FPGA IP catalog. For more details on the IP, refer to F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide.

To work with this IP, create an F-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IP and a secondary profiles for each of the data rate you want to support. For instance, a triple-rate SDI which supports 3 different data rates – 270 Mbps (SD-SDI), 1.485 Gbps (HD-SDI) and 2.97 Gbps (3G-SDI), requires 1 PHY base profile and 2 secondary profiles with 3 different data rate configurations. However, since 3G-SDI and SD-SDI can share the same PHY configuration in SDI II Intel® FPGA IP’s transceiver handling, only 1 secondary profile has to be created in F-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IP on the RX side. For the TX side, the single rate version of F-Tile PMA/FEC Direct PHY Intel® FPGA IP instance is used as the IP does not require reconfiguration between data rates, because the IP is doing oversampling. Refer to TX Sample topic for more information. However, if your design requires two reference clocks switching for NTSC and PAL rates, F-Tile PMA/FEC Direct PHY Multirate Intel® FPGA IP is required to connect the TX PLL reference clock to another clock port.

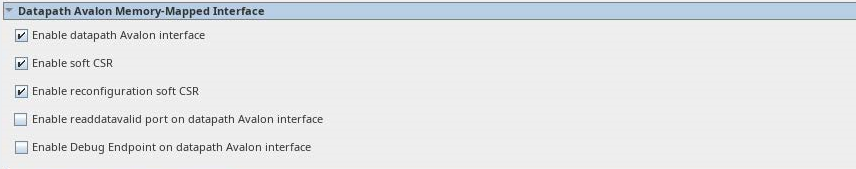

- Enable datapath Avalon interface

- Enable soft CSR

- Enable reconfiguration soft CSR

After instantiating these instances, which act as a profile instance, you must connect the reconfig_pdp clock (you can share the same clock as i_csr_clk port from the F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP) and reset ports, and terminate the Avalon® memory-mapped interface ports. You must include the following assignments in the project’s .qsf file to define the reconfiguration group.

set_instance_assignment -name IP_RECONFIG_GROUP <your base profile ID> -to <Multirate PHY base profile instance> set_instance_assignment -name IP_COLOCATE F_TILE -from <Dynamic reconfig IP instance> -to <Multirate PHY base profile instance>

SDI II Intel® FPGA IP’s design example contains RTL modules of the reconfiguration controller, as well as an arbiter to interact between SDI II IP and the Dynamic Reconfiguration Suite IP. For more details on the RTL example, refer to F-Tile SDI II Intel® FPGA IP Design Example User Guide.