Visible to Intel only — GUID: aec1572136912881

Ixiasoft

Visible to Intel only — GUID: aec1572136912881

Ixiasoft

6.5.6.3. ADDR/CMD Reference Voltage/RESET Signal Routing Guidelines for Single Rank x 8 and R Rank x 16 Discrete (Component) Topologies

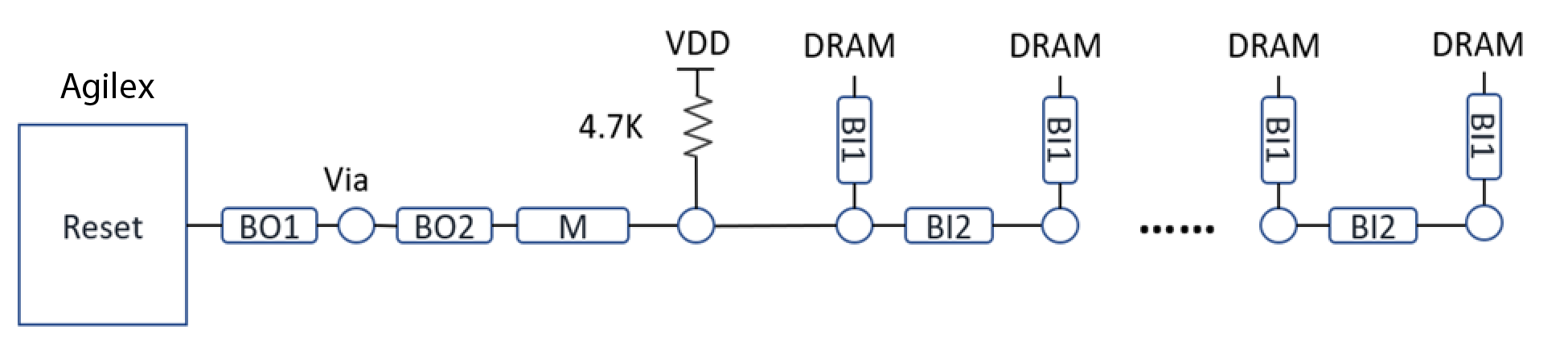

The following figure shows the RESET routing scheme, which you can apply to both single rank x 8 and single rank x16 topologies.

The Address/Command reference voltage input (VREF_CA) must track the VTT regulator output as closely as possible. There are two methods to achieve this:

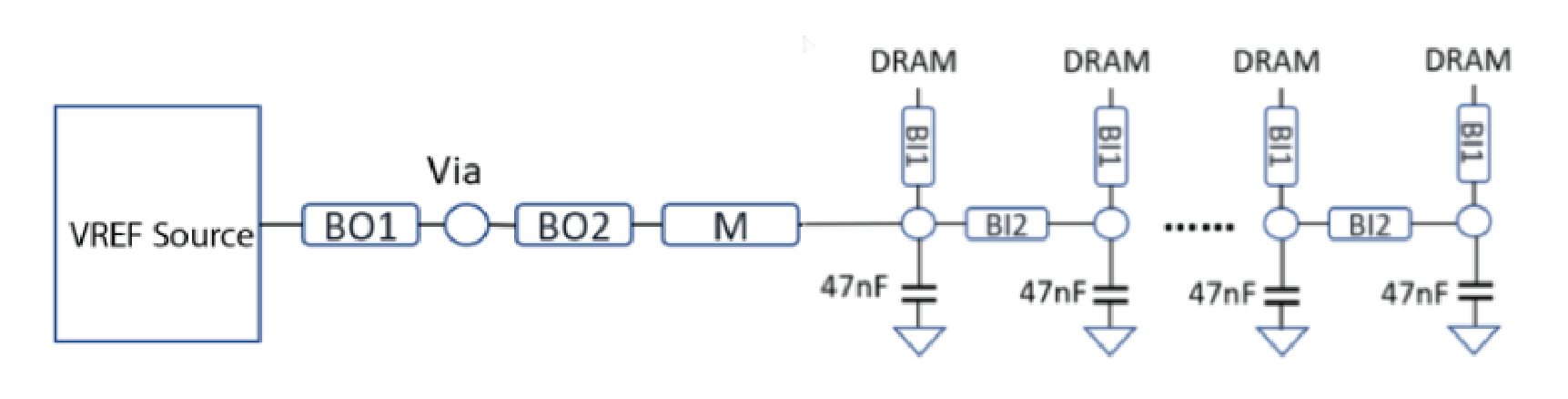

One method is to use a regulator that provides a dedicated tracking voltage reference output that can be connected directly to memory component VREF_CA inputs, as shown in the figure below.

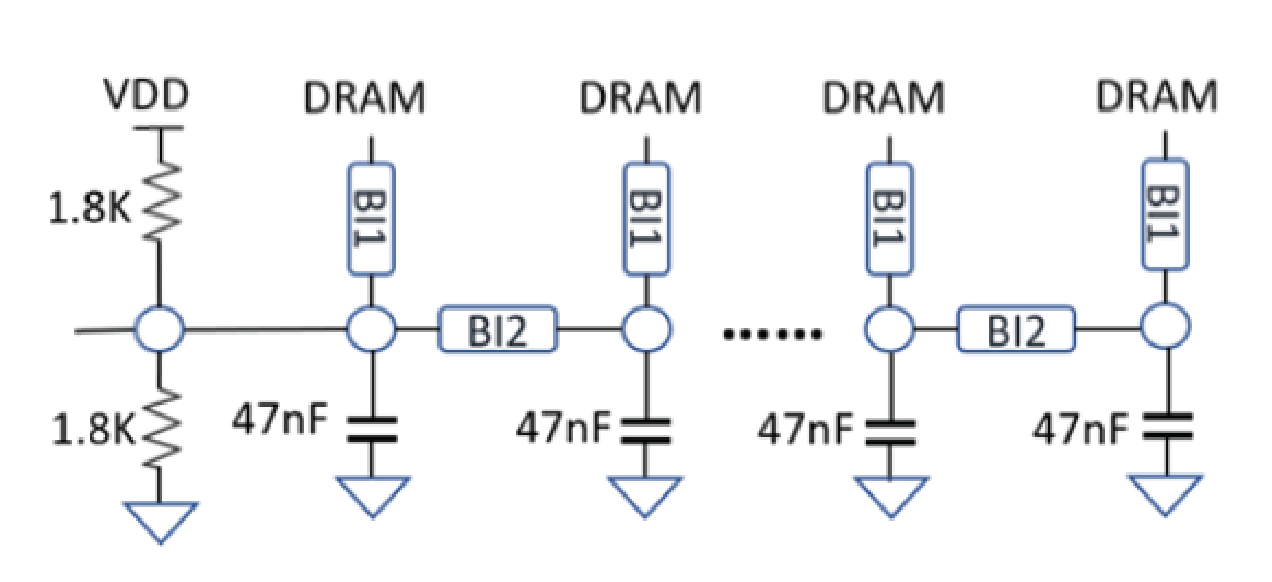

A second method is to create a voltage divider using precision resistors. Place the resistor network in a location that is likely to track IR losses on the VDD supply due to memory loading (that is, close to the VTT regulator or memory components, rather than next to the VDD regulator output). The following figure illustrates this configuration.

Intel® recommends using a PCB trace width of at least 10 mils for VREF_CA routing. The VREF_CA signal must have at least 3×h spacing (where h is the distance or height from the trace to the nearest reference plane) to other nearby signals on the same layer.