Visible to Intel only — GUID: sss1463109918783

Ixiasoft

Visible to Intel only — GUID: sss1463109918783

Ixiasoft

1.2.5.1.1. JESD204B Subsystem in Platform Designer

The JESD204B subsystem instantiates the following modules:

- JESD204B Intel® FPGA IP

- Reset sequencer

- Transceiver PHY reset controller

- Avalon® memory-mapped bridge

JESD204B IP

The generated design example is a self-contained system with its own JESD204B IP core instantiation that is separate from the IP core that is generated from the IP tab. The JESD204B IP base core and PHY layer connect to System Console through the Avalon® memory-mapped interconnect. The JESD204B IP core uses three separate Avalon® memory-mapped ports:

- Base core TX data path—For dynamic reconfiguration of the TX CSR parameters

- Base core RX data path—For dynamic reconfiguration of the RX CSR parameters

- PHY layer—For dynamic reconfiguration of transceiver PHY CSR

You can dynamically change the configuration of the JESD204B IP core base and PHY layers through TCL scripts using the System Console.

The structure of the design example varies depending on the values of these JESD204B IP core parameters:

- Data path:

- Duplex—Both TX and RX data paths and CSR interfaces present

- TX only—Only TX data path and CSR interface present

- RX only—Only RX data path and CSR interface present

- Transceiver dynamic reconfiguration mode:

- When enabled, transceiver PHY reconfiguration interface is present in the design example and connected the JTAG to Avalon® master bridge (System Console control) module.

- When disabled, transceiver PHY reconfiguration interface not present in design example.

Reset Sequencer

The reset sequencer is a standard Platform Designer component in the IP Catalog standard library. The reset sequencer generates the following system resets to reset various modules in the system:

- Core PLL reset—resets the core PLL

- Transceiver reset—resets the JESD204B IP core PHY module

- TX/RX JESD204B IP core CSR reset—resets the TX/RX JESD204B IP core CSRs

- TX/RX link reset—resets the TX/RX JESD204B IP core base module and transport layer

- TX/RX frame reset—resets the TX/RX transport layer, upstream and downstream modules

The reset sequencer has hard and soft reset options. The hard reset port connects to the global reset input pin in the top level design. The soft reset is activated via Avalon® memory-mapped interface by TCL scripts (System Console control). When you assert a hard or soft reset, the reset sequencer cycles through all the various module resets based on a pre-set sequence. The figure below illustrates the sequence and also shows how the reset sequencer output ports correspond to the modules that are being reset.

Transceiver PHY Reset Controller

The transceiver PHY reset controller is a standard Platform Designer component in the IP Catalog standard library. This module takes the transceiver PHY reset output from the reset sequencer and generates the proper analog and digital reset sequencing for the transceiver PHY module.

Avalon® Memory-Mapped Bridge

All the Avalon® memory-mapped submodules in the JESD204B subsystem are connected via Avalon® memory-mapped interconnect to a single Avalon® memory-mapped bridge. This bridge is the single interface for Avalon® memory-mapped communications into and out of the subsystem.

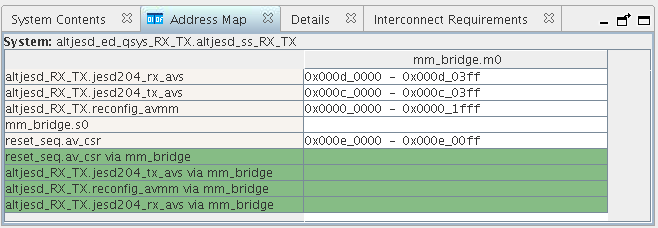

JESD204B Subsystem Address Map

Access the address map of the submodules in the JESD204B subsystem by clicking on the Address Map tab in the Platform Designer window.

JTAG to Avalon® Master Bridge

The JTAG to Avalon® master bridge is a standard Platform Designer component in the IP Catalog standard library. This module provides a connection between a host system and the Platform Designer system via the respective physical interfaces; JTAG on the host system end and Avalon® memory-mapped on the Platform Designer system end. Host systems can initiate Avalon® memory-mapped transactions by sending encoded streams of bytes via JTAG interface. The module supports reads and writes, but not burst transactions.