Visible to Intel only — GUID: mcl1620125170113

Ixiasoft

Visible to Intel only — GUID: mcl1620125170113

Ixiasoft

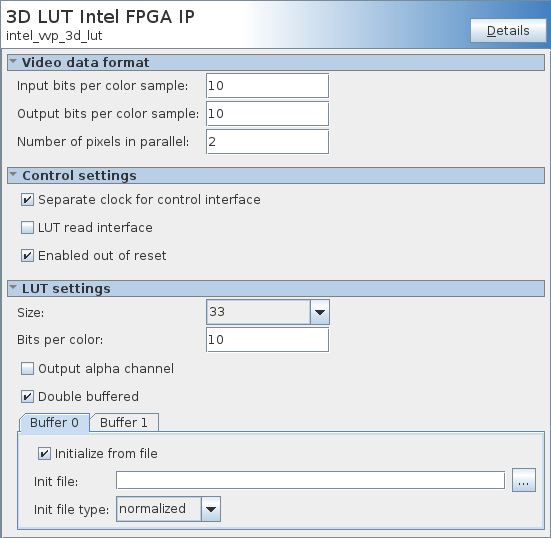

9.2. 3D LUT IP Parameters

| Name | Values | Description |

|---|---|---|

| Video data format | ||

| Number of pixels in parallel | 1 to 8 | Number of pixels transmitted every clock cycle. |

| Input bits per color sample | 8 to 16 | Number of bits per color sample at the input. |

| Output bits per color sample | 8 to 16 | Number of bits per color sample at the output. |

| Control settings | ||

| Separate clock for control interface | On or off | Turn on to run the run-time control interface on a different clock domain. |

| LUT read interface | On or off | Allows you to read LUT contents via the CPU interface. |

| Enabled out of reset | On or off |

|

| LUT settings | ||

| Size | 9, 17, 33, 65 | Size of each LUT dimension. |

| Bits per color | 8 to 16 | The number of bits per color in the LUT (LUT_DEPTH). |

| Output alpha channel | On or off | Turn on to add alpha channel to the LUT (RGBA). |

| Bypass alpha | 0 to 2 LUT_DEPTH -1 | The alpha value output in bypass mode. |

| Double buffered | On or off | Double the memory for seamless LUT programming and switching:

|

| Buffer 0 and Buffer 1 | ||

| Initialize from file | On or off | Turn on to initialize the LUT from the initialization file. |

| Init file | user file | Optional initialization file. |

| Init file type | normalized, integer | Type of coefficients in the initialization file:

|

LUT Initialization File

You can initialize each buffer of the LUT from reset by providing a compatible 3D LUT file to Init file in the GUI. The IP generation process converts the LUT file into RAM initialization .hex files that get built into the firmware during compilation. The script can read .cube format files, or any 3D LUT files that follow these conventions:

- RGB component order (must match the video stream’s order)

- Components change first from left to right, i.e. R first, G second, B third

- If you turn on alpha, you append the alpha value as a fourth component (RGBA)

- The data type must match the IP GUI parameter and may either be:

- normalized fixed- or floating-point numbers between 0.0 to 1.0

- integers between 0 and 2LUT_DEPTH-1 (e.g. 10-bit: 0 to 1023)

- The data type must be the same for the whole file

- Lines starting with # or any letter are ignored